Systems- and Networks-on-a-Chip

Betreuung:

Dr.-Ing. Stefan Wildermann

Paul Krüger, M.Sc.

Modulbeschreibung:

Systems- and Networks-on-a-Chip (2,5 ECTS)

Systems- and Networks-on-a-Chip für INF (5 ECTS)

Umfang:

2,5 ECTS (Vortrag + Handout) oder 5 ECTS für INF (Vortrag + Handout + Ausarbeitung)

Zeit und Ort:

nach Vereinbarung im Block gegen Ende der Vorlesungszeit

Vorbesprechung:

Ort und Zeit der Vorbesprechung wird noch bekannt gegeben.

Anmeldung:

Die Anmeldung erfolgt über StudOn.

Die Anzahl der Plätze ist begrenzt.

Seminarsprache:

Englisch

Beschreibung:

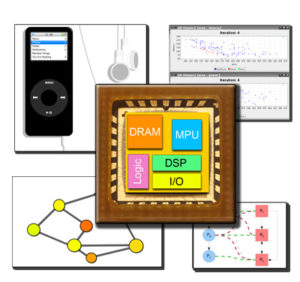

Eingebettete Systeme spielen im alltäglichen Leben eine immer größere Rolle. Gleichzeitig nimmt die Komplexität dieser Systeme immer weiter zu. Durch die heutige Technologie ist es möglich, Millionen, in naher Zukunft Milliarden von Transistoren auf einem Chip zu platzieren. Dies führt dazu, dass häufig das komplette eingebettete System, ein sogenanntes System-on-a-Chip (SoC), auf einem einzigen Chip realisiert werden kann. Die Vorteile einer verbesserten Performanz, niedrigerem Energieverbrauch sowie sinkenden Kosten sind dabei unter anderem durch die Wiederverwendung bestehender Komponenten bedingt. Eine der Herausforderungen bestehender SoCs besteht darin, eine korrekte und zuverlässige Kommunikation zwischen den Komponenten herzustellen. Aus diesem Grund wird den Komponenten eine netzwerkartige Kommunikation zur Verfügung gestellt, wodurch sogenannte Networks-on-a-Chip (NoCs) entstehen.Dieses Seminar beschäftigt sich mit der Problematik von Design, Synthese und Analyse bestehender und zukünftiger Systems- und Networks-on-a-Chip. Hierbei soll vor allem die Vereinbarkeit verschiedener Anforderungen an das System wie Kosten, Platz- und Energieverbrauch oder Zuverlässigkeit in den verschiedenen Phasen der Entwicklung betrachtet werden.

Themen: Die Themen werden im Rahmen der Vorbesprechung vorgestellt und vergeben.

Kontakt

Dr.-Ing. Stefan Wildermann

- Telefon: +49 9131 85-25161

- E-Mail: stefan.wildermann@fau.de

Paul Krüger, M. Sc.

- Telefon: +49 9131 85-25142

- E-Mail: paul.krueger@fau.de